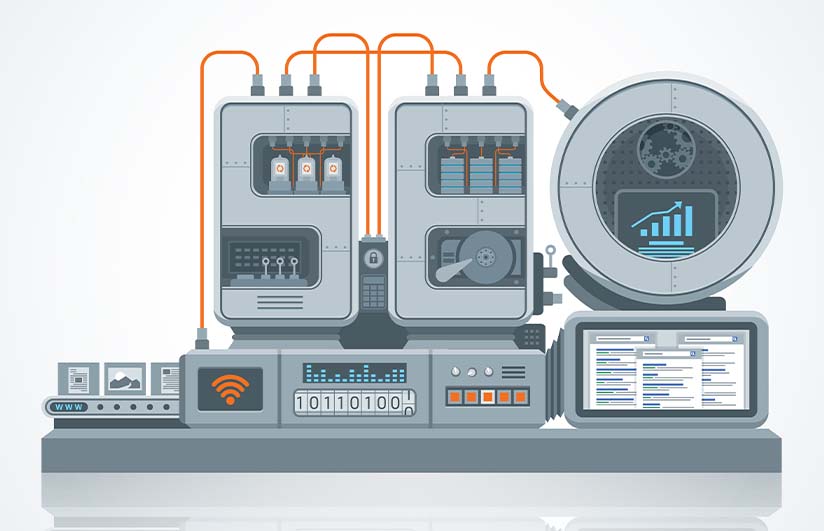

"MPS 모듈은 설계자동화분야에서 가장 보편적으로

사용 되는 실습장비로 업계 표준의 범용 장비입니다."

1. 모듈러 생산 시스템(Modular Production System)

생산 공정을 여러 개의 독립된 모듈로 나누어 각각의 모듈이 독립적으로 작동할 수 있도록 하는 생산 방식입니다. 이 시스템은 유연성과 효율성을 높이고, 변화하는 수요에 신속하게 대응할 수 있게 합니다.

2. 독립적인 모듈

각 모듈은 특정 작업이나 공정을 담당하며, 다른 모듈과 상호작용하지 않고도 독립적으로 운영될 수 있습니다.

모듈 간의 표준화된 인터페이스를 통해 쉽게 통합 및 교체가 가능합니다.

3. 유연성

생산 라인을 쉽게 재구성할 수 있어 다양한 제품을 효율적으로 생산할 수 있습니다.새로운 제품이나 공정을 추가할 때 전체 시스템을 재구성할 필요 없이 필요한 모듈만 추가하면 됩니다.

4. 확장성

생산량 증가에 따라 필요한 모듈을 추가함으로써 생산 능력을 쉽게 확장할 수 있습니다.초기 투자 비용을 절감하고, 생산 수요 변화에 유연하게 대응할 수 있습니다.

5. 효율성

각 모듈이 독립적으로 최적화될 수 있어 전체 생산 공정의 효율성을 높일 수 있습니다.생산 중단 없이 유지보수나 업그레이드를 수행할 수 있습니다.